駕馭先進封裝的奈米級視野:GBS smartWLI 檢測方案

量測實例表面粗糙度標準 Halle KNT 4070 Ra=25 nm

專為 CoWoS、玻璃基板與 Hybrid Bonding 製程打造,以 GPU 極速運算突破量測極限

在精密製造與品質檢測中,您是否也面臨這些挑戰?

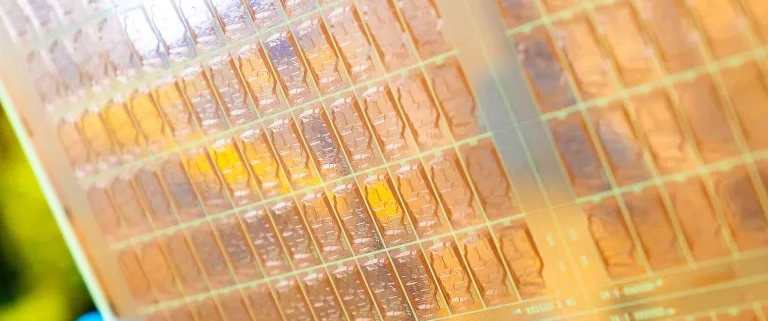

1. CoWoS 中介層 (Interposer) 與微凸塊 (Micro-bump) 量測

CoWoS 技術的核心在於將運算晶片與記憶體整合於矽中介層 (Interposer) 上,實現極致效能。

挑戰

為了達成高密度連接,Micro-bump (微凸塊) 變得極小且密集,其高度一致性 (Coplanarity) 決定了良率。

smartWLI 解決方案

smartWLI 專精於 Micro-bump 高度全檢,單次掃描即可精確分析視野內數百個 Micro-bump 的高度一致性。比起傳統檢測,我們能更精確抓出高度異常的凸塊,避免封裝後的接觸不良 (Open) 或短路 (Short),這是 CoWoS 製程中良率把關的關鍵一環。

Microbump

2. 平整度的極限:玻璃基板 (Glass Substrate) 檢測

玻璃基板因具備高穩定性與平整度,正成為先進封裝的新寵。

玻璃基板雖整體平整,但在微觀下的表面品質直接影響高頻訊號傳輸與線路附著力。

挑戰

為了實現超細線寬(L/S),玻璃表面必須達到極致的光滑,任何微觀粗糙都可能造成線路斷裂或剝離。

smartWLI 解決方案

利用白光干涉技術擅長量測光滑表面的特性,我們能精確分析玻璃基板的 Ra (平均粗糙度) 與 Rq (均方根粗糙度)。

不同於測量大範圍翹曲的設備,smartWLI 提供的是微觀下的表面品質保證,確保基板符合先進封裝的製程標準。

3. 掌控「奈米」的平整:Hybrid Bonding 鍵合面量測

Hybrid Bonding 要求銅墊與介電層之間達到原子級的平整接合。混合鍵合的成敗,取決於晶圓表面原子級的平整度。

挑戰

CMP 製程後的 Cu Dishing (銅凹陷)、Protrusion (突起) 及 Dielectric Erosion (介電質侵蝕) 必須控制在奈米範圍內,任何表面

形貌的異常都會導致鍵合空洞 (Void)。

smartWLI 解決方案

憑藉 0.1 nm 的垂直解析度,smartWLI 專精於鍵合前的表面計量,它專注於捕捉金屬銅墊與介電層表面的極微小高低差,確保兩者在物理接合前已達到完美的幾何條件。

解決方案:smartWLI 的核心優勢

smartWLI 系列結合 GPU 平行運算與 D-EPSI 演算法,不僅在高反射與傾斜面上維持高水平解析度與垂直解析度,更透過 smartSTITCH 校正演算法,消除 XY 平台誤差,讓量測結果更準確且更穩定。AQC 噪訊濾除技術自動剔除受干擾像素點,提升訊號品質能夠清楚擷取輪廓。配合 smartVIS3D 軟體整合,自動化量測流程省時省工。

- GPU 平行運算:速度比傳統 CPU 快上百倍加速全檢,產能與精度兼得,即時生成 3D 表面輪廓。

面對 CoWoS 產能緊繃的壓力,smartWLI 利用 GPU 平行運算將檢測速度提升百倍, - 8MP 高解析奈米級精度:兼顧水平與垂直解析度,確保數據真實可靠

- 高反光 / 斜面適應性:即使是高反光或傾斜的複雜表面,也能維持穩定測量,低 na 大收光可接受角

- smartSTITCH 演算法:獨有演算法增加訊號接收能力,自動補償 XY 平台誤差,量測結果更完整,可量測高深寬比物體

- AQC 品質控制:自動剔除干擾像素,降低噪訊,數據更乾淨,無須用濾波器,不影響水平解析

其他實例

- 晶圓與封裝零件:微小突起 / 凹陷的精確量測

- 光學鏡片:從拋光到塗層後的瑕疵檢測、微鏡片陣列瑕疵檢測等

- 電子元件:錫球檢測

黑矽晶表面

微鏡片陣列